# **Product Specifications**

| Customer    | STANDARD           |

|-------------|--------------------|

| Description | 9.7" TFT EPD Panel |

| Model Name  | E2969CS081         |

| Date        | 2019/10/28         |

| Doc. No.    | 1P225-00           |

| Revision    | 01                 |

| Customer Approval |                                                                                   |         |  |  |  |

|-------------------|-----------------------------------------------------------------------------------|---------|--|--|--|

|                   |                                                                                   |         |  |  |  |

|                   |                                                                                   |         |  |  |  |

| Date              |                                                                                   |         |  |  |  |

|                   | represents that the product specifications, ty in the specifications are accepted | testing |  |  |  |

| Design Engineering     |                               |                       |  |

|------------------------|-------------------------------|-----------------------|--|

| Approval               | Check                         | Design                |  |

| <b>養</b> 2019.10.28 朝玄 | 陳<br>2019.10.28<br>家 <b>荃</b> | 柯<br>2019.10.28<br>建宏 |  |

4F, No. 28, Chuangye Rd., Tainan Science Park, Tainan City 74144, Taiwan (R.O.C.)

Tel: +886-6-279-5399 Fax: +886-6-505-5300

Rev.: 01 Page: 1 of 30 Date: 2019/10/28

#### Copyright

Pervasive Displays Incorporated All rights reserved.

This document is the exclusive property of Pervasive Displays Inc. (PDI) and shall not be reproduced or copied or transformed to any other format without prior permission of PDI. (PDI Confidential)

本資料為龍亭新技股份有限公司專有之財產,非經許可,不得複製、翻印或轉變成其他形式使用。

龍亭新技股份有限公司 Pervasive Displays Inc.

4F, No. 28, Chuangye Rd., Tainan Science Park, Tainan City 74144, Taiwan (R.O.C.)

Tel: +886-6-279-5399

http://www.pervasivedisplays.com

Rev.: 01 Page: 2 of 30 Date: 2019/10/28

#### **Table of Contents**

| Re  | vision H | History                                   | 6  |  |

|-----|----------|-------------------------------------------|----|--|

| Glo | ssary (  | of Acronyms                               | 7  |  |

| 1   | Gener    | al Description                            | 8  |  |

|     | 1.1      | Overview                                  | 8  |  |

|     | 1.2      | Features                                  | 8  |  |

|     | 1.3      | Applications                              | 8  |  |

|     | 1.4      | General Specifications                    | 9  |  |

|     | 1.5      | Mechanical Specifications                 | 10 |  |

| 2   | Absol    | ute Maximum Ratings                       | 12 |  |

|     | 2.1      | Absolute Ratings of Environment           | 12 |  |

|     | 2.2      | Reliability Test Item                     | 13 |  |

|     | 2.3      | Product Warranty                          | 13 |  |

| 3   |          |                                           |    |  |

|     | 3.1      | Absolute Maximum Ratings of Panel         | 14 |  |

|     | 3.2      | Recommended Operation Conditions of Panel | 14 |  |

| 4   | Applic   | ation Circuit Block Diagram               | 16 |  |

| 5   | Termi    | nal Pin Assignment & Reference Circuit    | 17 |  |

|     | 5.1      | Terminal Pin Assignment                   | 17 |  |

|     | 5.2      | Reference Circuit                         | 20 |  |

| 6   | Optica   | al Characteristics                        | 21 |  |

|     | 6.1      | Measurement Conditions                    | 21 |  |

|     | 6.2      | Optical Specifications                    | 21 |  |

|     | 6.3      | Ghosting                                  | 24 |  |

| 7   | Packir   | ng                                        | 25 |  |

| 8   | Preca    | utions                                    | 27 |  |

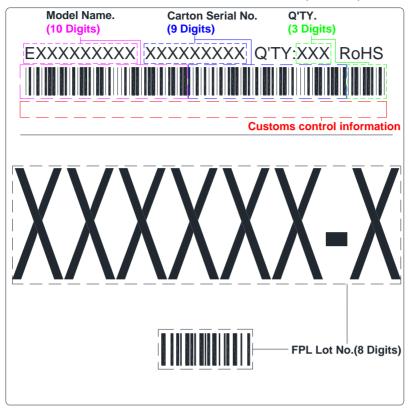

| 9   | Defini   | tion of Labels                            | 29 |  |

#### **List of Figures**

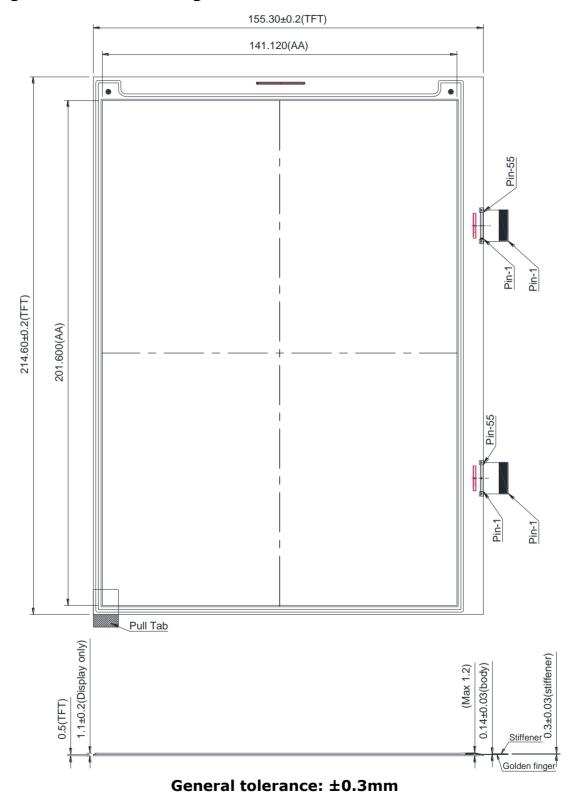

| Figure 1-1 | EPD Drawing                                           | 11 |

|------------|-------------------------------------------------------|----|

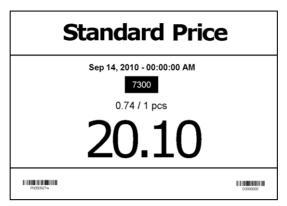

| Figure 3-1 | Test Pattern of Panel                                 | 15 |

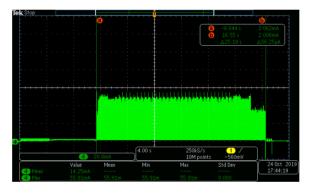

| Figure 3-2 | Image Update Current Profile                          | 15 |

| Figure 3-3 | Current Measurement                                   | 15 |

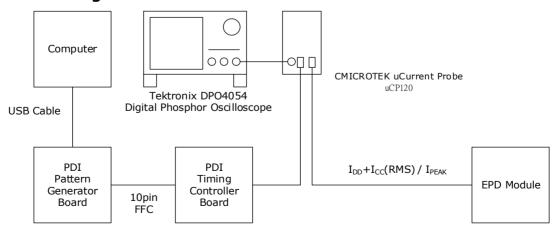

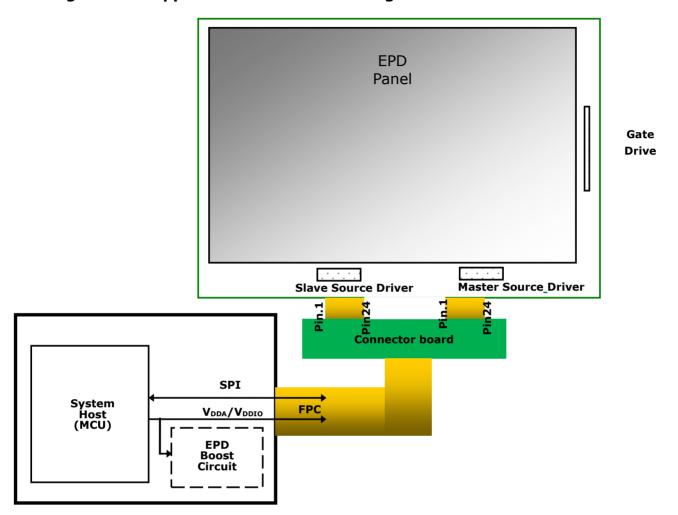

| Figure 4-1 | Application Circuit Block Diagram                     | 16 |

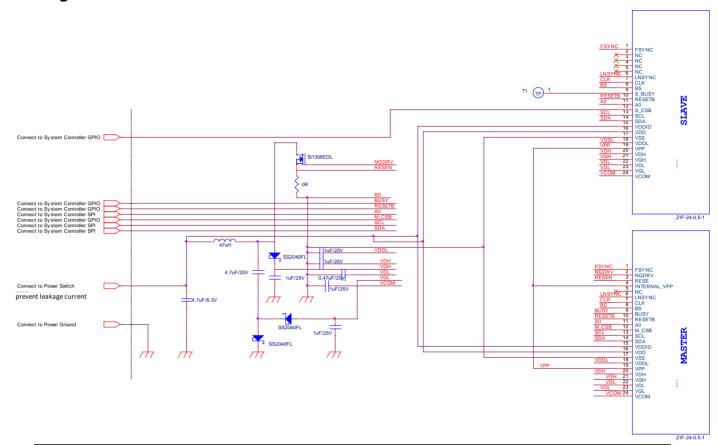

| Figure 5-1 | EPD Reference Circuit                                 | 20 |

| Figure 6-1 | Optical Measurement                                   | 22 |

| Figure 6-2 | Definition of Viewing Angle to Measure Contrast Ratio | 23 |

| Figure 7-1 | Packing Diagram                                       | 25 |

| Figure 9-1 | Model Labels                                          | 29 |

| Figure 9-2 | Definition of Model Labels                            | 29 |

| Figure 9-3 | Carton Label                                          | 30 |

| Figure 9-4 | Pallet Label                                          | 30 |

#### **List of Tables**

| Table 1-1 | General Specification                     | 9  |

|-----------|-------------------------------------------|----|

|           | EPD Mechanical Specification              |    |

| Table 1-3 | FPC Specification                         | 10 |

| Table 2-1 | Absolute Ratings of Environment           | 12 |

| Table 2-2 | Reliability Test Items                    | 13 |

| Table 3-1 | Absolute Maximum Ratings of Panel         | 14 |

| Table 3-2 | Recommended Operation Conditions of Panel | 14 |

| Table 5-1 | Terminal Pin Assignment (Master FPC)      | 17 |

| Table 5-1 | Terminal Pin Assignment (Slave FPC)       | 18 |

| Table 6-1 | Optical Measurement Conditions            | 21 |

| Table 6-2 | Optical Measurement with D65 light source | 21 |

| Table 6-3 | Measurement of Ghosting                   | 24 |

## **Revision History**

| Version | Date       | Page<br>(New) | Section | Description                |

|---------|------------|---------------|---------|----------------------------|

| 01      | 2019/10/28 | All           | All     | Specification first issued |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

|         |            |               |         |                            |

## **Glossary of Acronyms**

COG Chip on Glass

EPD Electrophoretic Display (e-Paper Display)

EPD Panel EPD

FPC Flexible Printed Circuit

FPL Front Plane Laminate

IIS Incoming Inspection Standard

ISTA International Safe Transit Association

PDI Pervasive Displays Incorporated

SPI Serial Peripheral Interface

TCon Timing Controller

TFT Thin Film Transistor

Rev.: 01 Page: 7 of 30 Date: 2019/10/28

## 1 General Description

#### 1.1 Overview

This is a 9.7" a-Si TFT active matrix Electronic Paper Display (EPD) module. The module has such high resolution (121 dpi) that it is able to easily display fine patterns. Due to its bi-stable nature, the EPD module requires very little power to update and needs no power to maintain an image.

#### 1.2 Features

- a-Si TFT active matrix Electronic Paper Display (EPD)

- Resolution: 672 x 960

- Ultra low power consumption

- Super Wide Viewing Angle near 180°

- Extra thin & light

- SPI interface

- RoHS compliant

- Wide temperature support

## 1.3 Applications

- e-POP/Signage

- Electronic bulletins

- Office Automation

- Navigator

Rev.: 01 Page: 8 of 30 Date: 2019/10/28

#### 1.4 General Specifications

**Table 1-1 General Specification**

| Item              | Specification                    | Unit  | Note |

|-------------------|----------------------------------|-------|------|

| Outline Dimension | 155.3 (H) x 214.6 (V) x 1.1(T)   | mm    | (1)  |

| Active Area       | 141.12 (H) x 201.6 (V)           | mm    |      |

| Driver Element    | a-Si TFT active matrix           | -     |      |

| FPL               | Aurora Mb                        | -     |      |

| Pixel Number      | 672 x 960                        | pixel |      |

| Pixel Pitch       | 0.210 x 0.210 (121 dpi)          | mm    |      |

| Pixel Arrangement | Vertical stripe                  | -     |      |

| Display Colors    | Black/White                      | -     |      |

| Surface Treatment | Anti-Glare                       | -     |      |

| Driver IC         | Source (IST7132) / Gate (HX8695) |       |      |

Note (1): Not including the FPC.

Rev.: 01 Page: 9 of 30 Date: 2019/10/28

### 1.5 Mechanical Specifications

**Table 1-2 EPD Mechanical Specification**

| Item       |               | Min.  | Тур.  | Max.  | Unit | Note |

|------------|---------------|-------|-------|-------|------|------|

|            | Horizontal(H) | 155.1 | 155.3 | 155.5 | mm   |      |

| Glass Size | Vertical(V)   | 214.4 | 214.6 | 214.8 | mm   |      |

|            | Thickness(T)  | 1.0   | 1.1   | 1.2   | mm   | (1)  |

| Weight     |               | -     | 61.5  | 1     | g    |      |

Note (1): Not including the Masking Film.

**Table 1-3 FPC Specification**

| Item          | Pin numbers | Pitch (mm) | Connector                        | Note |

|---------------|-------------|------------|----------------------------------|------|

| Golden Finger | 24          | 0.5        | HRS FH34SRJ 24S<br>or Compatible | (1)  |

Note (1): HRS FH34SRJ 24S is 24-pins connectors. The 24 pins are used to connect FPC pads of EPD. There are two FPCs on EPD panel. Please refer PDI demo kit for detailed connection.

Rev.: 01 Page: 10 of 30 Date: 2019/10/28

Figure 1-1 EPD Drawing

## 2 Absolute Maximum Ratings

#### 2.1 Absolute Ratings of Environment

**Table 2-1 Absolute Ratings of Environment**

| Item                          | Cymbol           | Value |      | Unit  | Nata        |  |

|-------------------------------|------------------|-------|------|-------|-------------|--|

| Item                          | Symbol           | Min.  | Max. | Ullic | Note        |  |

| Storage Temperature           | T <sub>ST</sub>  | -20   | +60  | ٥C    | (1),(3)     |  |

| Storage Humidity              | H <sub>ST</sub>  | 40    | 70   | %RH   | (1),(3)     |  |

| Operating Ambient Temperature | T <sub>OP</sub>  | 0     | +50  | ٥C    | (1),(2),(4) |  |

| Operating Ambient Humidity    | H <sub>OP</sub>  | 40    | 70   | %RH   | (1),(2),(4) |  |

| Optimal Storage Temperature   | T <sub>OST</sub> | -10   | 35   | ٥C    | (1),(3)     |  |

| Optimal Storage Humidity      | H <sub>OST</sub> | 40    | 60   | %RH   | (1),(3)     |  |

#### Note (1):

- (a) 70 %RH Max. (Ta  $\leq$  40 °C), where Ta is ambient temperature.

- (b) No condensation and no frost in absolute ratings of Environment.

- Note (2): The temperature of panel display surface area should be 0 °C Min. and 50 °C Max. Refresh time depends on operation temperature.

- Note (3): E Ink Material is Moisture and UV sensitive. The absolute rating operating environments describes the boundary conditions for updating the display while the absolute rating storage environment describe the boundary conditions for a display not updating. While displays are rated to perform according to specification for the warranty period at the absolute specified operating environment, the better the storage condition, the better the E Ink displays will perform. Similar to other moisture and UV sensitive components, we recommend that our displays be stored in temperature and humidity control environments, and whenever possible, under above defined Optimal Storage Condition, away from sunlight, to optimize their performance.

- Note (4): The performance of EPD may be degraded under sunlight. Please customer consults PDI if customer wants to use EPD under sunlight.

Rev.: 01 Page: 12 of 30 Date: 2019/10/28

#### 2.2 Reliability Test Item

**Table 2-2 Reliability Test Items**

| Item                                   | Test Condition                                                                     | Remark    |

|----------------------------------------|------------------------------------------------------------------------------------|-----------|

| High Temperature Operation             | 50 $^{\circ}$ / 30 %RH for 240h                                                    | (1) (2)   |

| Low Temperature Operation              | 0 ℃ for 240h                                                                       | (1) (2)   |

| High Temperature/Humidity<br>Operation | 40 $^{\circ}$ / 70 %RH for 240h                                                    | (1) (2)   |

| High Temperature Storage               | 60 ℃ / 40 %RH for 240h                                                             | (1)(2)(3) |

| Low Temperature Storage                | -20 ℃ for 240h                                                                     | (1)(2)(3) |

| High Temperature/Humidity<br>Storage   | 60 ℃ / 80 %RH for 240h                                                             | (1)(2)(3) |

| Thermal Cycles ( Non-operation )       | 1 Cycle:-20 $^{\circ}$ C/30min $\rightarrow$ 60 $^{\circ}$ C/30min, for 100 Cycles | (1)(2)(3) |

| Package Drop Test                      | Drop from 97cm. ( ISTA )<br>1 corner, 3 edges, 6 sides. One drop for<br>each.      | (1)(2)(3) |

| Package Random Vibration Test          | 1.15Grms, 1Hz ~ 200Hz. ( ISTA )                                                    | (1)(2)(3) |

Note (1): No condensation and no frost during test. End of test, function, mechanical, and optical shall be satisfied with product specification and IIS.

## 2.3 Product Warranty

Warranty conditions have to be negotiated between PDI and individual customers. PDI provides 13 months warranty for all products which are purchased from PDI.

Rev.: 01 Page: 13 of 30 Date: 2019/10/28

Note (2): The test result and judgment are based on PDI's 1bit driving waveform, driving fixture and driving system.

Note (3): Stay white pattern for storage and non-operation test.

#### 3 Electrical Characteristics

## 3.1 Absolute Maximum Ratings of Panel

**Table 3-1 Absolute Maximum Ratings of Panel**

| Parameter     | Cymbol            | ١    | /alue | Unit  | Noto                              |  |

|---------------|-------------------|------|-------|-------|-----------------------------------|--|

| Parameter     | Symbol            | Min  | Max   | Ullit | Note                              |  |

| Digital Power | $V_{\text{DDIO}}$ | -0.3 | 5.0   | V     |                                   |  |

| Analog Power  | $V_{DD}$          | -0.3 | 5.0   | V     |                                   |  |

| Ground        | V <sub>SS</sub>   | -    |       | -     | Connect V <sub>SS</sub> to Ground |  |

$T_a = 25 \pm 2 \, {}^{\circ}\text{C}$

### 3.2 Recommended Operation Conditions of Panel

**Table 3-2 Recommended Operation Conditions of Panel**

| Parameter                          |           | Cymbal                                 |                      | Value           |                      | l loit   | Note                                           |

|------------------------------------|-----------|----------------------------------------|----------------------|-----------------|----------------------|----------|------------------------------------------------|

| Paran                              | ieter     | Symbol                                 | Min                  | Тур             | Max                  | Unit     | Note                                           |

| VDDIO<br>operation                 | -         | V <sub>DDIO</sub> ,<br>V <sub>DD</sub> | 2.3                  | 3.0             | 3.3                  | V        |                                                |

| Input                              | High      | $V_{\mathrm{IH}}$                      | 0.8V <sub>DDIO</sub> | ı               | $V_{\text{DDIO}}$    | <b>V</b> | V -V                                           |

| Voltage                            | Low       | $V_{\mathrm{IL}}$                      | $V_{SS}$             | -               | 0.2V <sub>DDIO</sub> | V        | $V_{DDIO}=V_{DD}$                              |

| Output                             | High      | V <sub>OH</sub>                        | 0.8V <sub>DDIO</sub> | -               | $V_{\text{DDIO}}$    | V        | $V_{DDIO}=V_{DD}=2.4V$<br>$I_{OUT}=1$ mA       |

| Voltage                            | Low       | V <sub>OL</sub>                        | V <sub>SS</sub>      | -               | 0.2V <sub>DDIO</sub> | V        | $V_{DDIO}=V_{DD}=2.4V$<br>$I_{OUT}=-1$ mA,     |

| Input C<br>(standard<br>bit_ched   | d price / | $I_{CC}$                               | -                    | 14.3 /<br>26.4  | -                    | mA       |                                                |

| Peak C<br>(standard<br>bit_ched    | d price / | ${ m I}_{\sf PEAK}$                    |                      | 55.9/<br>104.6  |                      | mA       | (1), (2), (3)<br>FPI lot: VEU025<br>Q'ty: 5pcs |

| Power Con<br>(standard<br>bit_ched | d price / | -                                      |                      | 358.9/<br>665.0 |                      | mAs      |                                                |

$T_a = 25 \pm 2 \, {}^{\circ}\text{C}$

Rev.: 01 Page: 14 of 30 Date: 2019/10/28

Note (1):

Figure 3-1 Test Pattern of Panel

These currents are tested with PDI test jig.

Note (2):  $V_{DDIO}=V_{DD}=3.0V$

Figure 3-2 Image Update Current Profile

Note (3):

Figure 3-3 Current Measurement

<sup>\*</sup>Set oscilloscope filter to 250MHz and record length to 10M points.

Rev.: 01 Page: 15 of 30 Date: 2019/10/28

## 4 Application Circuit Block Diagram

Figure 4-1 Application Circuit Block Diagram

Rev.: 01 Page: 16 of 30 Date: 2019/10/28

## 5 Terminal Pin Assignment & Reference Circuit

## **5.1 Terminal Pin Assignment**

**Table 5-1 Terminal Pin Assignment (Master FPC)**

| No. | Signal       | Type | Connected to                   | Function                                                                                                                                                     |

|-----|--------------|------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FSYNC        | I/O  | Slave FSYNC                    | Cascade line frame sync                                                                                                                                      |

| 2   | NGDRV        | 0    | Power MOSFET<br>Driver control | This pin is the N-Channel MOSFET Gate Drive Control.                                                                                                         |

| 3   | RESE         | I    | Booster Control Input          | This pin is the Current Sense Input for the Control Loop.                                                                                                    |

| 4   | INTERNAL_VPP | Р    | VPP PIN & Slave FPC            | MTP power internal                                                                                                                                           |

| 5   | NC           | С    | -                              | NC                                                                                                                                                           |

| 6   | LNSYNC       | I/O  | Slave LNSYNC                   | Cascade line sync                                                                                                                                            |

| 7   | CLK          | I/O  | Slave CLK                      | Cascade clock                                                                                                                                                |

| 8   | BS           | I    | VSS                            | This pin is setting panel interface.                                                                                                                         |

| 9   | M_BUSY       | 0    | Device Busy Signal             | This pin is Busy state output pin of the master chip. When Busy is Low, the operation of the chip should not be interrupted, and Command should not be sent. |

| 10  | RESETB       | I    | System Reset                   | This pin is reset signal input. Active Low.                                                                                                                  |

| 11  | A0           | I    | VDDIO or VSS                   | This pin is Data/Command control.                                                                                                                            |

| 12  | M_CSB        | I    | VDDIO or VSS                   | This pin is the Master chip select.                                                                                                                          |

| 13  | SCL          | I    | Data Bus                       | Serial communication clock input.                                                                                                                            |

| 14  | SDA          | I    | Data Bus                       | Serial communication data input/output.                                                                                                                      |

| 15  | VDDIO        | Р    | Power Supply                   | Power for interface logic pins & I/O. It should be connected with VDDIO.                                                                                     |

| 16  | VDD          | Р    | Power Supply                   | Power Supply for the chip.                                                                                                                                   |

| 17  | VSS          | Р    | Ground                         | Ground                                                                                                                                                       |

| 18  | VDDL         | С    | Capacitor                      | Internal regulator output A capacitor should be connected between VDDL and VSS.                                                                              |

Rev.: 01 Page: 17 of 30 Date: 2019/10/28

| No. | Signal | Туре | Connected to              | Function                                                                                                          |

|-----|--------|------|---------------------------|-------------------------------------------------------------------------------------------------------------------|

| 19  | VPP    | Р    | INTERNAL_VP&<br>Slave VPP | MTP power                                                                                                         |

| 20  | VDH    | O    | Capacitor                 | This pin is the Positive Source driving voltage. A stabilizing capacitor should be connected between VDH and VSS. |

| 21  | VGH    | С    | Capacitor                 | This pin is the Positive Gate driving voltage A stabilizing capacitor should be connected between VGH and VSS.    |

| 22  | VDL    | С    | Capacitor                 | This pin is the Negative Source driving voltage. A stabilizing capacitor should be connected between VDL and VSS. |

| 23  | VGL    | С    | Capacitor                 | This pin is the Negative Gate driving voltage. A stabilizing capacitor should be connected between VGL and VSS.   |

| 24  | VCOM   | С    | Capacitor                 | This pin is the VCOM driving voltage A stabilizing capacitor should be connected between VCOM and VSS.            |

## **Table 5-2 Terminal Pin Assignment (Slave FPC)**

| No. | Signal | Туре | Connected to       | Function                                                                                                                                                    |

|-----|--------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FSYNC  | I/O  | Master FSYNC       | Cascade line frame sync                                                                                                                                     |

| 2   | NC     | ı    | -                  | Not connected                                                                                                                                               |

| 3   | NC     | ı    | -                  | Not connected                                                                                                                                               |

| 4   | NC     | -    | -                  | Not connected                                                                                                                                               |

| 5   | NC     | -    | -                  | Not connected                                                                                                                                               |

| 6   | LNSYNC | I/O  | Master LNSYNC      | Cascade line sync                                                                                                                                           |

| 7   | CLK    | I/O  | Master CLK         | Cascade clock                                                                                                                                               |

| 8   | BS     | I    | VSS                | This pin is setting panel interface.                                                                                                                        |

| 9   | S_BUSY | 0    | Device Busy Signal | This pin is Busy state output pin of the slave chip. When Busy is Low, the operation of the chip should not be interrupted, and Command should not be sent. |

| 10  | RESETB | I    | System Reset       | This pin is reset signal input. Active Low.                                                                                                                 |

Rev.: 01 Page: 18 of 30 Date: 2019/10/28

| No. | Signal | Туре | Connected to | Function                                                                                                          |  |  |

|-----|--------|------|--------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| 11  | A0     | I    | VDDIO or VSS | This pin is Data/Command control.                                                                                 |  |  |

| 12  | S_CSB  | I    | VDDIO or VSS | This pin is the Slave chip select.                                                                                |  |  |

| 13  | SCL    | I    | Data Bus     | Serial communication clock input.                                                                                 |  |  |

| 14  | SDA    | I    | Data Bus     | Serial communication data input/output.                                                                           |  |  |

| 15  | VDDIO  | Р    | Power Supply | Power for interface logic pins & I/O. It should be connected with VDDIO.                                          |  |  |

| 16  | VDD    | Р    | Power Supply | Power Supply for the chip.                                                                                        |  |  |

| 17  | VSS    | Р    | Ground       | Ground                                                                                                            |  |  |

| 18  | VDDL   | С    | Capacitor    | Internal regulator output A capacitor should be connected between VDDL and VSS.                                   |  |  |

| 19  | VPP    | Р    | Master VPP   | MTP power                                                                                                         |  |  |

| 20  | VDH    | С    | Capacitor    | This pin is the Positive Source driving voltage. A stabilizing capacitor should be connected between VDH and VSS. |  |  |

| 21  | VGH    | С    | Capacitor    | This pin is the Positive Gate driving voltage A stabilizing capacitor should be connected between VGH and VSS.    |  |  |

| 22  | VDL    | С    | Capacitor    | This pin is the Negative Source driving voltage. A stabilizing capacitor should be connected between VDL and VSS. |  |  |

| 23  | VGL    | С    | Capacitor    | This pin is the Negative Gate driving voltage. A stabilizing capacitor should be connected between VGL and VSS.   |  |  |

| 24  | VCOM   | С    | Capacitor    | This pin is the VCOM driving voltage A stabilizing capacitor should be connected between VCOM and VSS.            |  |  |

Note:

Type: I: Input

O: Output

C: Capacitor

P: Power

Rev.: 01 Page: 19 of 30 Date: 2019/10/28

#### 5.2 Reference Circuit

Figure 5-1 EPD Reference Circuit

| Type       | Part                       | Quantity | Vendor   | Note |

|------------|----------------------------|----------|----------|------|

| Inductor   | 47uH 0.3A ETPRH3D16B-470M  | 1pc      | ARLITECH |      |

| Transistor | Si1308EDL SOT-23 N-Channel | 1pc      | Vishay   | (1)  |

| Diode      | SS2040FL SOD-123FL         | 3pcs     | PANJIT   | (2)  |

| Capacitors | 4.7uF/25V                  | 2pc      | -        |      |

| Capacitors | 1uF/25V                    | 5pcs     | -        |      |

| Capacitors | 0.47uF/25V                 | 1pcs     | -        |      |

| Resistors  | 0R ohm/1%                  | 1pc      | -        |      |

#### Note:

- (1) Si1308EDL is a N-Channel Power MOSFET. The specification of selection criteria are RDS<185 mohm (the lower the better), VGS<2.5V@Id=0.5A.

- (2) SS2040FL is a Schottky diode needs the Vf as lower as possible, 0.2 to 0.4V and the repetitive peak reverse voltage > 25V.

Rev.: 01 Page: 20 of 30 Date: 2019/10/28

## **6 Optical Characteristics**

#### **6.1 Measurement Conditions**

**Table 6-1 Optical Measurement Conditions**

| Item                | Symbol                              | Value | Unit |

|---------------------|-------------------------------------|-------|------|

| Ambient Temperature | Та                                  | 25±2  | oC   |

| Ambient Humidity    | На                                  | 50±10 | %RH  |

| Supply Voltage      | V <sub>DDIO</sub> & V <sub>DD</sub> | 3.0   | V    |

#### **6.2 Optical Specifications**

Table 6-2 Optical Measurement with D65 light source

| Thomas         | Cymbol |      | Rating |      | Llnit | Noto                                      |  |

|----------------|--------|------|--------|------|-------|-------------------------------------------|--|

| Item           | Symbol | Min. | Тур.   | Max. | Unit  | Note                                      |  |

| Contrast ratio | CR     | ı    | 18:1   | -    | ı     | $\theta x = \theta y = 0$ (1),(2),(4),(5) |  |

| Refresh time   | Tr     | ı    | 25.2   | 1    | sec   | (1),(3),(5)                               |  |

|                | L*     | ı    | 72.70  | -    | ı     | θx=θy=0<br>(1),(2),(5)                    |  |

| White state    | a*     | 1    | -3.12  | -    |       |                                           |  |

|                | b*     | -    | 2.88   | -    |       |                                           |  |

| Reflectance    | R%     | -    | 44.7   | -    | %     | (1),(2),(5)                               |  |

Rev.: 01 Page: 21 of 30 Date: 2019/10/28

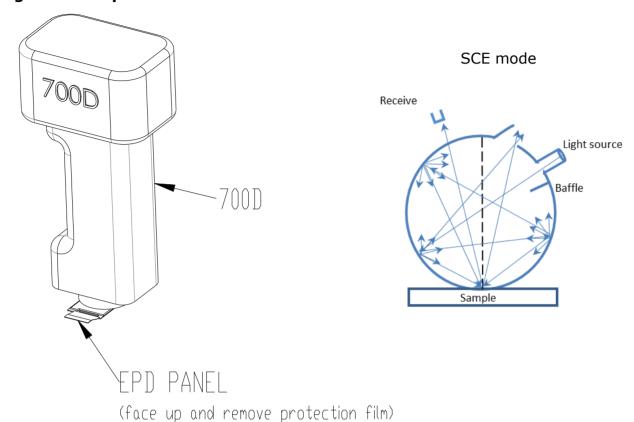

Note (1): Panel is driven by PDI waveform without masking film and optical measurement by CM-700D with D65 light source and SCE mode.

Figure 6-1 Optical Measurement

Rev.: 01 Page: 22 of 30 Date: 2019/10/28

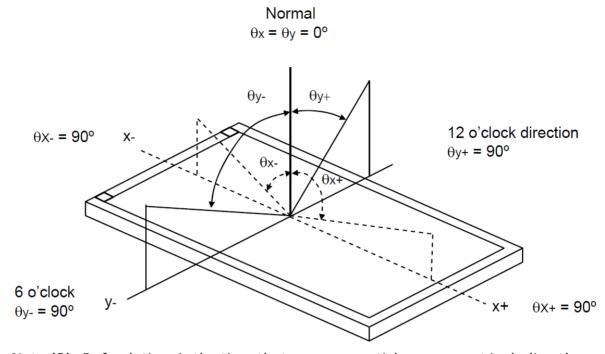

Note (2): Definition of Viewing Angle ( $\theta x$ ,  $\theta y$ ):

Figure 6-2 Definition of Viewing Angle to Measure Contrast Ratio

- Note (3): Refresh time is the time that e-paper particles move not including the power on and off time. The refresh time is measured at 25°C. The refresh time and contrast ratio varies due to different films, display performance requirements, and ambient temperatures.

- Note (4): Contrast ratio (C.R.): The Contrast ratio is calculated by the following expression. C.R. = (R% White) / (R% Black).

- Note (5): Optical data is measured at 60 seconds after refresh with PDI's global update procedure.

Rev.: 01 Page: 23 of 30 Date: 2019/10/28

#### 6.3 Ghosting

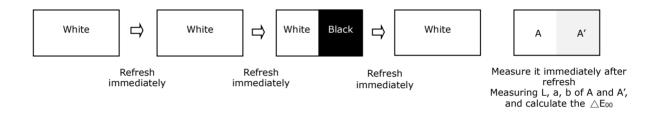

Below are two test methods to verify if ghosting is within an acceptable range. Test 1 and Test 2 use measured data to calculate color different,  $\triangle E_{00}$  (CIEDE 2000).

The condition of measurement is to follow "Table 6-1 Optical Measurement Conditions".

Test 1: White to Black Ghosting

Test 2: Black to White Ghosting

Table 6-3 Measurement of Ghosting

| Thomas         | Rating |      |      |  |  |

|----------------|--------|------|------|--|--|

| Item           | Min.   | Тур. | Max. |  |  |

| Test 1<br>△E₀₀ | -      | -    | 2    |  |  |

| Test 2<br>△E₀₀ | -      | -    | 2    |  |  |

Note: Panel is driven by PDI waveform without masking film and optical is measured by CM-700D with D65 light source and SCE mode.

Rev.: 01 Page: 24 of 30 Date: 2019/10/28

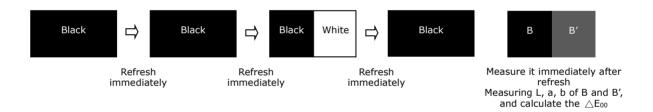

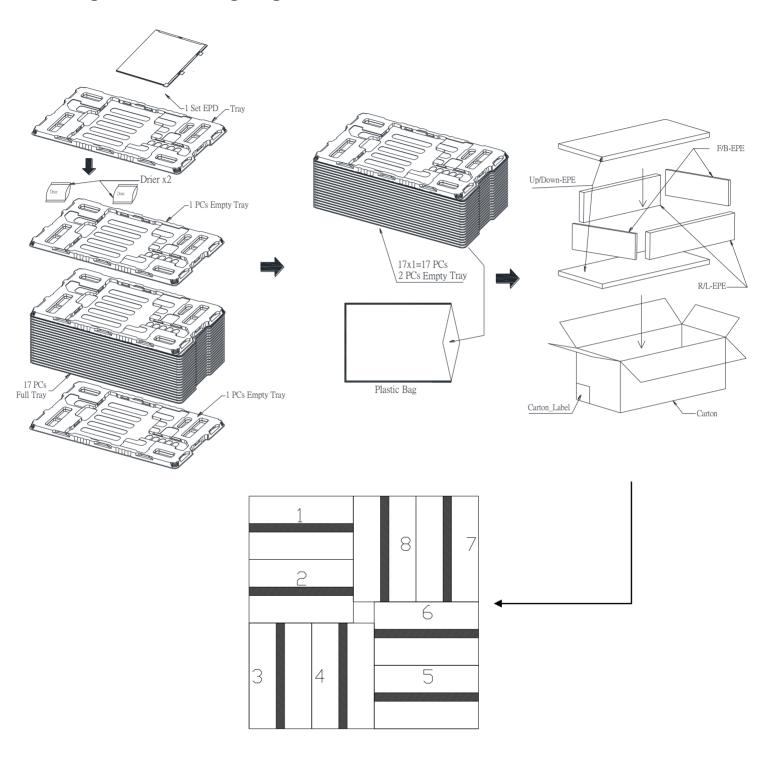

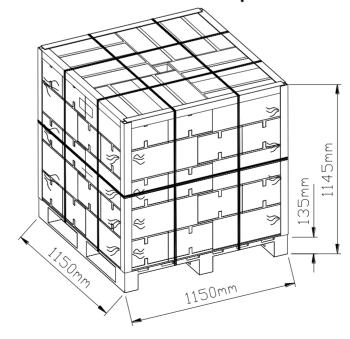

## 7 Packing

Figure 7-1 Packing Diagram

Rev.: 01 Page: 25 of 30 Date: 2019/10/28

17(pcs)x40(BOX)=680pcs

|       | 9.7" EPD BOX |  |  |  |

|-------|--------------|--|--|--|

| N.W.: | 1.05 Kg      |  |  |  |

| G.W.: | 4.53 Kg      |  |  |  |

# Sea / Land / Air Transportation

Rev.: 01 Page: 26 of 30 Date: 2019/10/28

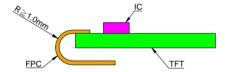

#### 8 Precautions

- (1) The EPD Panel / Module is manufactured from fragile materials such as glass and plastic, and may be broken or cracked if dropped. Please handle with care. Do not apply force such as bending or twisting to the EPD panel during assembly. Please put on gloves to handle EPD to avoid slash.

- (2) It is recommended to assemble or install EPD panels in a clean working area. Dust and oil may cause electrical shorts or degrade / scratch / den the protection sheet film.

- (3) Do not apply pressure to the EPD panel in order to prevent damaging it.

- (4) Do not connect or disconnect the interface connector while the EPD panel is in operation.

- (5) Please support the bezel with your finger while connecting the interface cable such as the FPC.

- (6) Do not stack the EPD panels / Modules.

- (7) Do not press the FPC on the glass edge or Pull FPC up / down to 90°.

- (8) Do not touch the FPC lead connector.

- (9) Do not touch IC bonding area. It may scratch TFT lead or damage IC function.

- (10) Wear a Wrist Strap (Grounding connect) when handling and during assembly. Semiconductor devices are included in the EPD Panel / Module and they should be handled with care to prevent any electrostatic discharge (ESD). (An Ion Fan may be needed in assembly operation to reduce ESD risk.)

- (11) Keep the EPD Panel / Module in the specified environment and original packing boxes when storage in order to avoid scratching and keep original performance.

- (12) Do not disassemble or reassemble the EPD panel.

- (13) Use a soft dry cloth without chemicals for cleaning. Please don't press hard for cleaning because the surface of the protection sheet film is very soft and without hard coating. This behavior would make dent or scratch on protection sheet.

- (14) Please be mindful of moisture to avoid its penetration into the EPD panel, which may cause damage during operation.

- (15) It's low temperature operation product. Please be mindful the temperature different to make frost or dew on the surface of EPD panel. Moisture may penetrate into the EPD panel because of frost or dew on surface of EPD panel, and makes EPD panel damage.

- (16) If the EPD Panel / Module is not refreshed every 24 hours, a phenomena known as "Ghosting" or "Image Sticking" may occur. It is recommended that customer refreshed the ESL / EPD Tag every 24 hours in use case. It is recommended that customer ships or stores the ESL / EPD Tag with a completely white image to avoid this issue.

- (17) High temperature, high humidity, sunlight or fluorescent light may degrade the EPD panel's performance. Please do not expose the unprotected EPD panel to high temperature, high humidity, sunlight, or fluorescent for long periods of time.

- (18) The label ink used for marking the Panel ID number is erased easily by solvent. Please avoid using solvent to clean the EPD panel. It would be concerned for RMA.

- (19) The EPD / Module is vacuum packed with white image for shipment and storage.

- (20) Before approved by PDI and customer, products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- (21) PDI makes every attempt to ensure that its products are of high quality and reliability. However, contact PDI sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- (22) Design your application so that the product is used within the ranges guaranteed by PDI particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. PDI bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail safes, so that the equipment incorporating PDI product does not cause bodily injury, fire or other consequential damage due to operation of the PDI product.

- (23) This product is not designed to be radiation resistant.

- (24) Please keep  $R \ge 1.0$ mm when bend for assembly.

Rev.: 01 Page: 28 of 30 Date: 2019/10/28

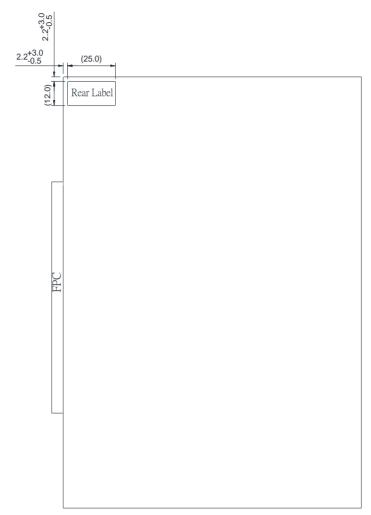

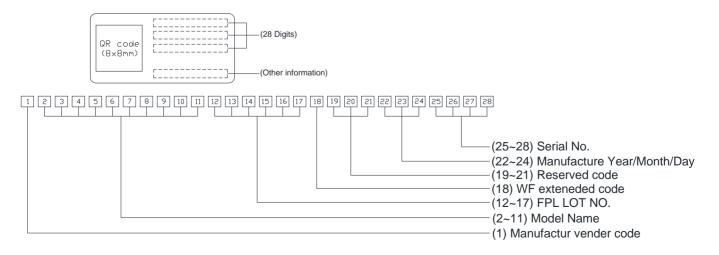

#### 9 Definition of Labels

Figure 9-1 Model Labels

Figure 9-2 Definition of Model Labels

Rev.: 01 Page: 29 of 30 Date: 2019/10/28

Figure 9-3 Carton Label

Bar Code=Model Name.+Carton Serial No.+Q'TY.(Code 128)

Carton Label

Figure 9-4 Pallet Label

Bar Code=Model Name.+Pallet Serial No.+Q'TY.(22 Digits)

## **Pallet Label**

Rev.: 01 Page: 30 of 30 Date: 2019/10/28