# Application Note for 12" Mono With the cascaded IST7136 iTC (MTP LUT)

| Description | Interface for the 12" Mono EPD with the cascaded IST7136 iTC |

|-------------|--------------------------------------------------------------|

| Date        | 2020/10/5                                                    |

| Doc. No.    |                                                              |

| Revision    | 01                                                           |

4F, No. 28, Chuangye Rd., Tainan Science Park, Tainan City 74144, Taiwan (R.O.C.)

Tel: +886-6-279-5399 Fax: +886-6-270-5857

Rev.: 01 Page: 1 of 26 Date: 2020/10/5

## **Table of Contents**

| 1   | Gener    | al Description         | 3  |

|-----|----------|------------------------|----|

|     | 1.1      | Overview               | 3  |

|     | 1.2      | Panel drawing          | 4  |

|     | 1.3      | FPC interface          | 5  |

|     |          | EPD Driving Flow Chart |    |

|     | 1.5      | SPI Timing Format      | 10 |

|     | 1.6      | Read MTP data          | 13 |

| 2   |          | on COG driver          |    |

| 3   | Initial  | ize COG Driver         | 15 |

|     | 3.1      | Initial flow chart     |    |

|     | 3.2      | Send image to the EPD  | 16 |

|     |          | DC/DC soft-start       |    |

| 4   | Send     | updating command       | 22 |

| 5   | Turn-o   | off DC/DC              | 23 |

| Re  | vision H | History                | 25 |

| Glo | ossarv ( | of Acronyms            | 26 |

# 1 General Description

#### 1.1 Overview

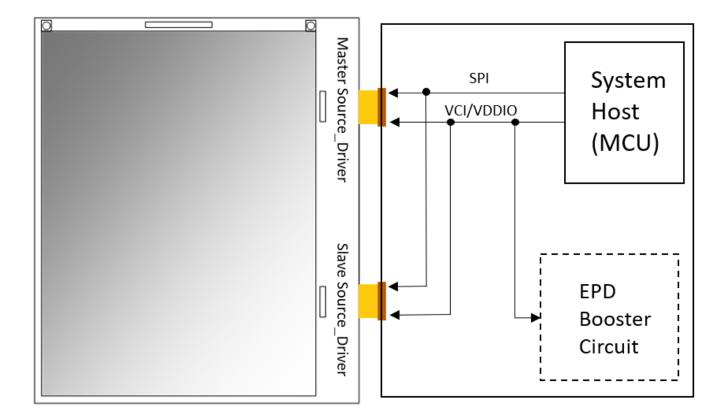

The document introduces how to drive the 12" EPD with the cascaded IST7136. The EPD has embedded the Tcon function. The major control interface of the driver is SPI. The host sends both the setting commands and the display image to driver through the SPI bus.

Rev.: 01 Page: 3 of 26 Date: 2020/10/5

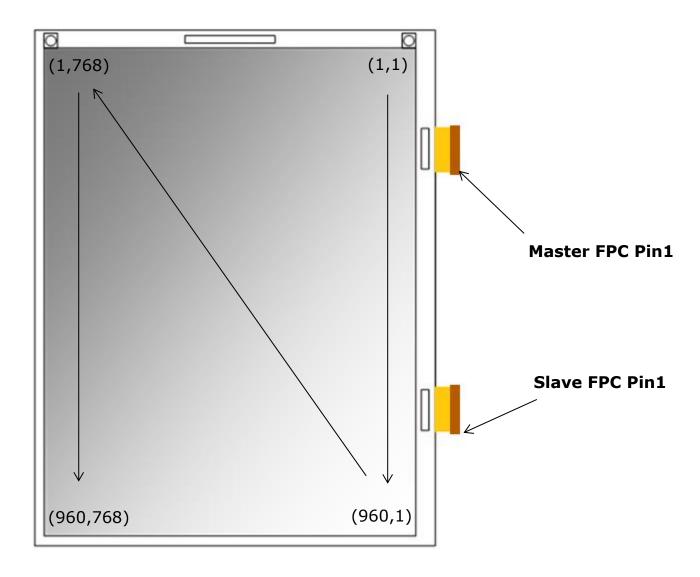

# 1.2 Panel drawing

# 1.3 interface

The 12" EPD was mounted two source drivers. They are Master and Slave role respectively and share the same SPI with separate CS.

The pin assignment of FPC are as follows, the pitch of FPC is 0.5mm.

#### 1.3-1 Master FPC Pin Define

| No. | Signal       | Type | Connected to                   | Function                                                                                                                                                     |

|-----|--------------|------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FSYNC        | I/O  | Slave FSYNC                    | Cascade line frame sync                                                                                                                                      |

| 2   | NGDRV        | 0    | Power MOSFET<br>Driver control | This pin is the N-Channel MOSFET Gate Drive Control.                                                                                                         |

| 3   | RESE         | I    | Booster Control Input          | This pin is the Current Sense Input for the Control Loop.                                                                                                    |

| 4   | INTERNAL_VPP | Р    | VPP PIN & Slave FPC            | MTP power internal                                                                                                                                           |

| 5   | NC           | С    | -                              | NC                                                                                                                                                           |

| 6   | LNSYNC       | I/O  | Slave LNSYNC                   | Cascade line sync                                                                                                                                            |

| 7   | CLK          | I/O  | Slave CLK                      | Cascade clock                                                                                                                                                |

| 8   | BS           | I    | VSS                            | This pin is setting panel interface.                                                                                                                         |

| 9   | M_BUSY       | 0    | Device Busy Signal             | This pin is Busy state output pin of the master chip. When Busy is Low, the operation of the chip should not be interrupted, and Command should not be sent. |

| 10  | RESETB       | I    | System Reset                   | This pin is reset signal input. Active Low.                                                                                                                  |

| 11  | A0           | I    | VDDIO or VSS                   | This pin is Data/Command control.                                                                                                                            |

| 12  | M_CSB        | I    | VDDIO or VSS                   | This pin is the Master chip select.                                                                                                                          |

| 13  | SCL          | I    | Data Bus                       | Serial communication clock input.                                                                                                                            |

| 14  | SDA          | I    | Data Bus                       | Serial communication data input/output.                                                                                                                      |

| 15  | VDDIO        | Р    | Power Supply                   | Power for interface logic pins & I/O. It should be connected with VDDIO.                                                                                     |

| 16  | VDD          | Р    | Power Supply                   | Power Supply for the chip.                                                                                                                                   |

| 17  | VSS          | Р    | Ground                         | Ground                                                                                                                                                       |

| 18  | VDDL         | С    | Capacitor                      | Internal regulator output A capacitor should be connected between VDDL and VSS.                                                                              |

Rev.: 01 Page: 5 of 26 Date: 2020/10/5

| No. | Signal | Туре | Connected to               | Function                                                                                                          |

|-----|--------|------|----------------------------|-------------------------------------------------------------------------------------------------------------------|

| 19  | VPP    | Р    | INTERNAL_VPP&<br>Slave VPP | MTP power                                                                                                         |

| 20  | VDH    | С    | Capacitor                  | This pin is the Positive Source driving voltage. A stabilizing capacitor should be connected between VDH and VSS. |

| 21  | VGH    | С    | Capacitor                  | This pin is the Positive Gate driving voltage A stabilizing capacitor should be connected between VGH and VSS.    |

| 22  | VDL    | С    | Capacitor                  | This pin is the Negative Source driving voltage. A stabilizing capacitor should be connected between VDL and VSS. |

| 23  | VGL    | С    | Capacitor                  | This pin is the Negative Gate driving voltage. A stabilizing capacitor should be connected between VGL and VSS.   |

| 24  | VCOM   | С    | Capacitor                  | This pin is the VCOM driving voltage<br>A stabilizing capacitor should be connected<br>between VCOM and VSS.      |

## 1.3-2 Slave FPC Pin Define

| No. | Signal | Туре | Connected to       | Function                                                                                                                                                    |  |

|-----|--------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | FSYNC  | I/O  | Master FSYNC       | Cascade line frame sync                                                                                                                                     |  |

| 2   | NC     | -    | -                  | Not connected                                                                                                                                               |  |

| 3   | NC     | -    | -                  | Not connected                                                                                                                                               |  |

| 4   | NC     | -    | -                  | Not connected                                                                                                                                               |  |

| 5   | NC     | -    | -                  | Not connected                                                                                                                                               |  |

| 6   | LNSYNC | I/O  | Master LNSYNC      | Cascade line sync                                                                                                                                           |  |

| 7   | CLK    | I/O  | Master CLK         | Cascade clock                                                                                                                                               |  |

| 8   | BS     | I    | VSS                | This pin is setting panel interface.                                                                                                                        |  |

| 9   | S_BUSY | 0    | Device Busy Signal | This pin is Busy state output pin of the slave chip. When Busy is Low, the operation of the chip should not be interrupted, and Command should not be sent. |  |

| 10  | RESETB | I    | System Reset       | This pin is reset signal input. Active Low.                                                                                                                 |  |

| 11  | A0     | I    | VDDIO or VSS       | This pin is Data/Command control.                                                                                                                           |  |

| 12  | S_CSB  | I    | VDDIO or VSS       | This pin is the Slave chip select.                                                                                                                          |  |

| 13  | SCL    | I    | Data Bus           | Serial communication clock input.                                                                                                                           |  |

Rev.: 01 Page: 6 of 26 Date: 2020/10/5

| No. | Signal | Туре | Connected to | Function                                                                                                          |  |

|-----|--------|------|--------------|-------------------------------------------------------------------------------------------------------------------|--|

| 14  | SDA    | I    | Data Bus     | Serial communication data input/output.                                                                           |  |

| 15  | VDDIO  | Р    | Power Supply | Power for interface logic pins & I/O. It should be connected with VDDIO.                                          |  |

| 16  | VDD    | Р    | Power Supply | Power Supply for the chip.                                                                                        |  |

| 17  | VSS    | Р    | Ground       | Ground                                                                                                            |  |

| 18  | VDDL   | С    | Capacitor    | Internal regulator output A capacitor should be connected betwee VDDL and VSS.                                    |  |

| 19  | VPP    | Р    | Master VPP   | MTP power                                                                                                         |  |

| 20  | VDH    | С    | Capacitor    | This pin is the Positive Source driving voltage. A stabilizing capacitor should be connected between VDH and VSS. |  |

| 21  | VGH    | С    | Capacitor    | This pin is the Positive Gate driving voltage A stabilizing capacitor should be connected between VGH and VSS.    |  |

| 22  | VDL    | С    | Capacitor    | This pin is the Negative Source driving voltage. A stabilizing capacitor should be connected between VDL and VSS. |  |

| 23  | VGL    | С    | Capacitor    | This pin is the Negative Gate driving voltage. A stabilizing capacitor should be connected between VGL and VSS.   |  |

| 24  | VCOM   | С    | Capacitor    | This pin is the VCOM driving voltage A stabilizing capacitor should be connected between VCOM and VSS.            |  |

Rev.: 01 Page: 7 of 26 Date: 2020/10/5

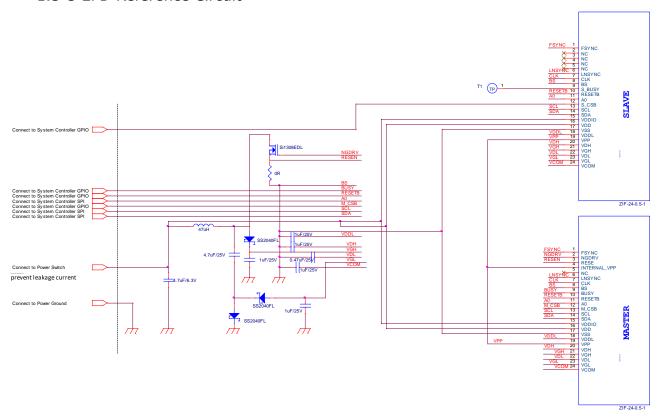

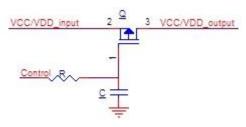

#### 1.3-3 EPD Reference Circuit

Rev.: 01 Page: 8 of 26 Date: 2020/10/5

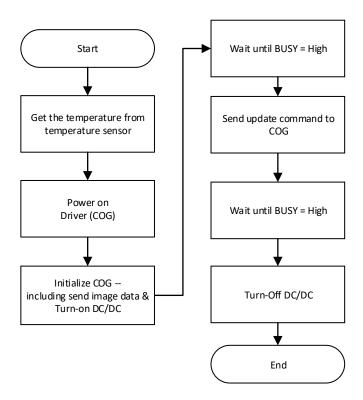

# 1.4 EPD Driving Flow Chart

The flowchart below provides an overview of the necessary actions to update the EPD. The steps below refer to the detailed descriptions in the respective sections.

Rev.: 01 Page: 9 of 26 Date: 2020/10/5

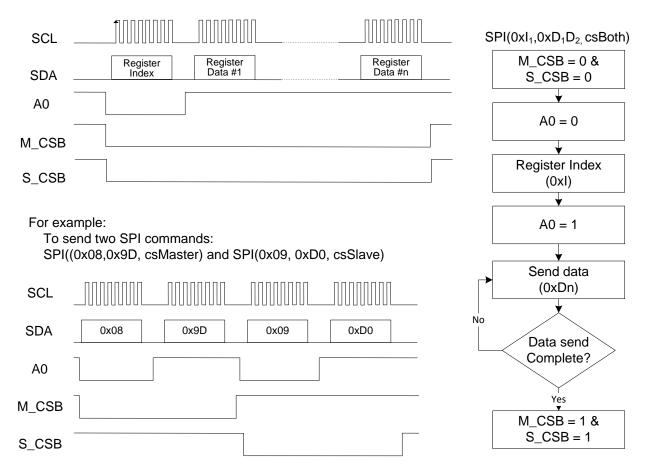

# 1.5 SPI Timing Format

SPI commands are used to communicate between the MCU and the COG Driver. The SPI format used differs from the standard in that two way communications are not used. When setting up the SPI timing, PDI recommends verify both the SPI command format and SPI command timing in this section.

The maximum clock speed of the display is **5MHz**.

Below is a description of the SPI Format:

$SPI(0xI, 0xD_1, 0xD_2, ..., 0xD_n, csDS)$

Where:

I is the Register Index and the length is 1 byte  $D_{1\sim n}$  is the Register Data. The Register Data length is variously.

The csDS indicates this command is delivered to which driver or both.

csMaster: only deliver to Master driver csSlave: only deliver to Slave driver csBoth: deliver to both Master and Slave

• When SPI sends the Index, the A0 has to pull LOW. When sends the data, the A0 has to pull HIGH. The next page is the detail flow chart.

Rev.: 01 Page: 10 of 26 Date: 2020/10/5

SPI command signals and flowchart:

If register data is larger than two bytes, you must input data continuously without setting Register Index again.

Rev.: 01 Page: 11 of 26 Date: 2020/10/5

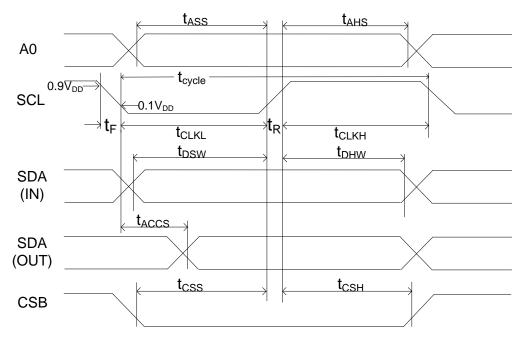

# SPI command timing

#### **SPI DATA-IN**

| Item                   | Symbol             | Min. | Тур. | Max. | Unit | Remark |

|------------------------|--------------------|------|------|------|------|--------|

| Clock Cycle Time       | $t_{\text{cycle}}$ | 200  | -    | -    | ns   |        |

| Chip Select Setup Time | t <sub>CSS</sub>   | 90   | -    | -    | ns   |        |

| Chip Select Hold Time  | t <sub>CSH</sub>   | 90   | -    | -    | ns   |        |

| Write Data Setup Time  | $t_{DSW}$          | 90   | -    | -    | ns   |        |

| Write Data Hold Time   | t <sub>DHW</sub>   | 90   | -    | -    | ns   |        |

| A0 Setup Time          | t <sub>ASS</sub>   | 90   | -    | -    | ns   |        |

| A0 Hold Time           | t <sub>AHS</sub>   | 90   | -    | -    | ns   |        |

| Clock Low Time         | t <sub>CLKL</sub>  | 90   | -    | -    | ns   |        |

| Clock High Time        | t <sub>CLKH</sub>  | 90   | -    | -    | ns   |        |

| Rise Time [10% ~ 90%]  | t <sub>R</sub>     | -    | -    | 15   | ns   |        |

| Fall Time [90% ~ 10%]  | t <sub>F</sub>     | -    | -    | 15   | ns   |        |

#### SPI DATA-OUT (read)

| Item                   | Symbol             | Min. | Тур. | Max. | Unit | Remark |

|------------------------|--------------------|------|------|------|------|--------|

| Clock Cycle Time       | t <sub>cycle</sub> | 600  | -    | -    | ns   |        |

| Chip Select Setup Time | t <sub>CSS</sub>   | 400  | -    | -    | ns   |        |

| Chip Select Hold Time  | t <sub>CSH</sub>   | 150  | -    | -    | ns   |        |

| Read access time       | t <sub>ACCS</sub>  | -    | -    | 200  | ns   |        |

| A0 Setup Time          | t <sub>ASS</sub>   | 90   | -    | -    | ns   |        |

| A0 Hold Time           | t <sub>AHS</sub>   | 90   | -    | -    | ns   |        |

| Clock Low Time         | t <sub>CLKL</sub>  | 400  | -    | -    | ns   |        |

| Clock High Time        | $t_{CLKH}$         | 150  | -    | -    | ns   |        |

| Rise Time [10% ~ 90%]  | t <sub>R</sub>     | -    | -    | 15   | ns   |        |

| Fall Time [90% ~ 10%]  | t <sub>F</sub>     | -    | -    | 15   | ns   |        |

VCC = 2.3 to 3.6V Temp = 0 to  $+50^{\circ}$ C

Rev.: 01 Page: 12 of 26 Date: 2020/10/5

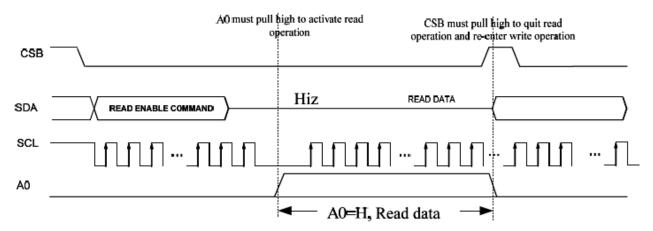

## 1.6 Read OTP data

The 128-bytes section of OTP have saved the user-defined data(OTP address from 0x0EE8 to 0x0F67) that includes the information of the display and soft-start parameters. The section will introduce how to read out the data through the SPI.

Note: 1. After read enable command is set, SDA must set Hiz, and A0 set high to active read operation

2. When read operation is done, CSB must set high once to quit read operation.

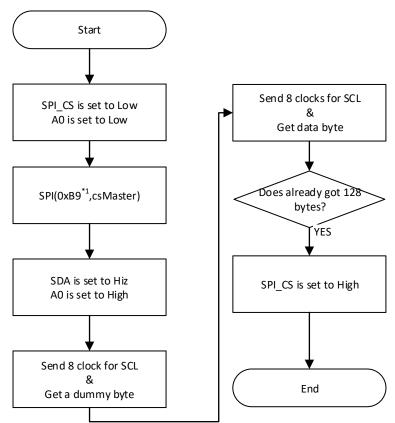

# Read operation of 4-Line SPI

#### Note:

1. Use command 0xB9 to read OTP data from OTP address 0x0EE8 to 0x0F67.

Rev.: 01 Page: 13 of 26 Date: 2020/10/5

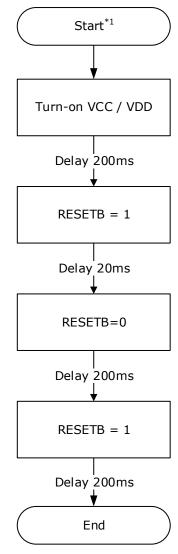

# 2 Power on COG driver

This flowchart describes power sequence for driver chip.

#### Note:

#### 1. Start

Initial State:

VCC/VDD, RESETB, M\_CSB, S\_CSB, SDA, SCL = 0 In order to the inrush current will cause other issue. It is recommended to add soft-start when VCC/VDD is turned on.

VCC/VDD soft-start

Rev.: 01 Page: 14 of 26 Date: 2020/10/5

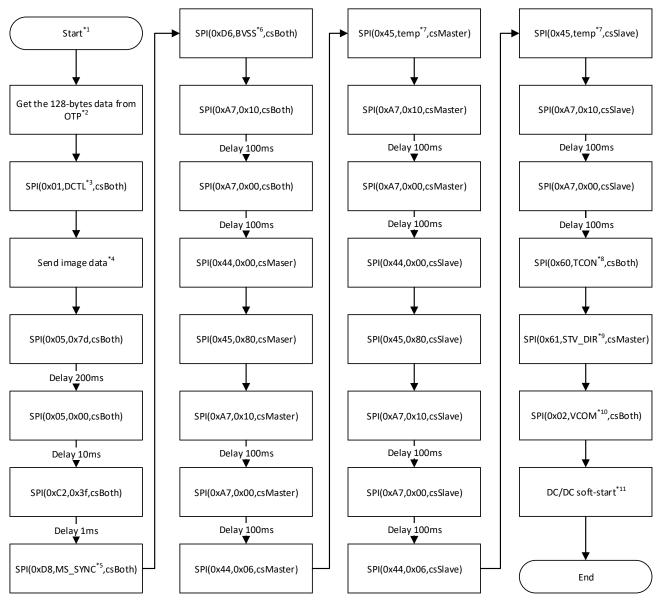

# 3 Initialize COG Driver

#### 3.1 Initial flow chart

#### Note:

- 1. Start: Follow the end of the power on sequence

- 2. Please refer to section 1.6 to get the 128-bytes of the user-defined.

- 3. DCTL is read from 0x10 of OTP memory

- 4. Please refer to section 3.2

- 5. MS SYNC is read from 0x1D of OTP memory

- 6. BVSS is read from 0x1E of OTP memory

- 7. The data represents the temperature value. The acceptable range of temperature is -40  $\sim$  87°C and 0.5°C per step. Such as,

$-40^{\circ}C = 0x00$ ,

$\theta$ °C =  $\theta$ x5 $\theta$ ,

$25^{\circ}C = 0x82$ ,

$87^{\circ}C = 0xFE$

- 8. TCON is read from 0x0B of OTP memory.

- 9. STV\_DIR is read from 0x1C of OTP memory

- 10. VCOM is read from 0x11 of OTP memory

- 11. Please refer to section 3.3

Rev.: 01 Page: 15 of 26 Date: 2020/10/5

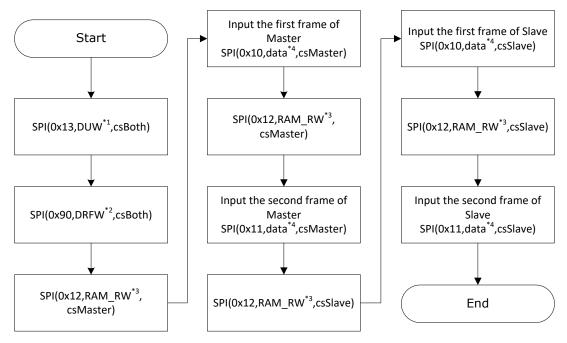

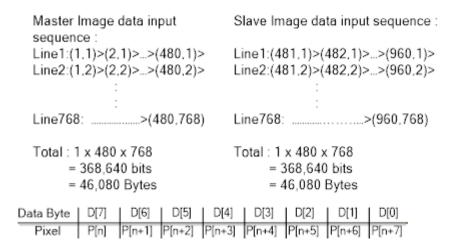

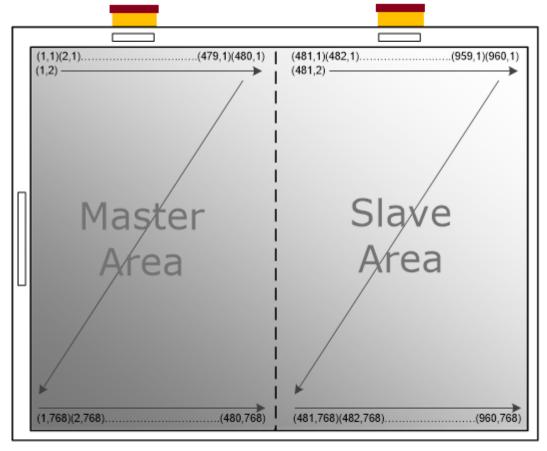

# 3.2 Send image to the EPD

This section describes how to send image data into COG which will be displayed on the display.

#### Note:

- 1, **DUW**: there is 6 bytes' data that are read from 0x16 ~ 0x1B of OTP memory.

- 2. **DRFW**: there is 4 bytes' data that are read from 0x0C ~ 0x0F of OTP memory.

- 3. **RAM\_RW**: there is 3 bytes' data that are read from  $0x13 \sim 0x15$  of OTP memory.

- 4. The data of totally have 46,080 bytes, please refer to next page to send the data.

Rev.: 01 Page: 16 of 26 Date: 2020/10/5

Both First and Second frame data need to be send into Master and Slave driver respectively each updating. The index of the First frame is 0x10 and the Second frame is 0x11.

### Image format

The data of image frame, one bit represents 1 pixel. (e.g. the first byte represents the  $1_{st} \sim 8_{th}$  pixels of the first line, the second byte represents the  $9_{th} \sim 16_{th}$  pixels of the first line, ..... and so on).

Rev.: 01 Page: 17 of 26 Date: 2020/10/5

#### First frame

In this frame, the data "1" represents black color pixel and the data "0" represents both white color pixel.

| Data | Pixel<br>Color |

|------|----------------|

| 1    | Black          |

| 0    | White          |

#### Second frame

The frame is a dummy frame just need to feed 46,080 bytes 0x00

Rev.: 01 Page: 18 of 26 Date: 2020/10/5

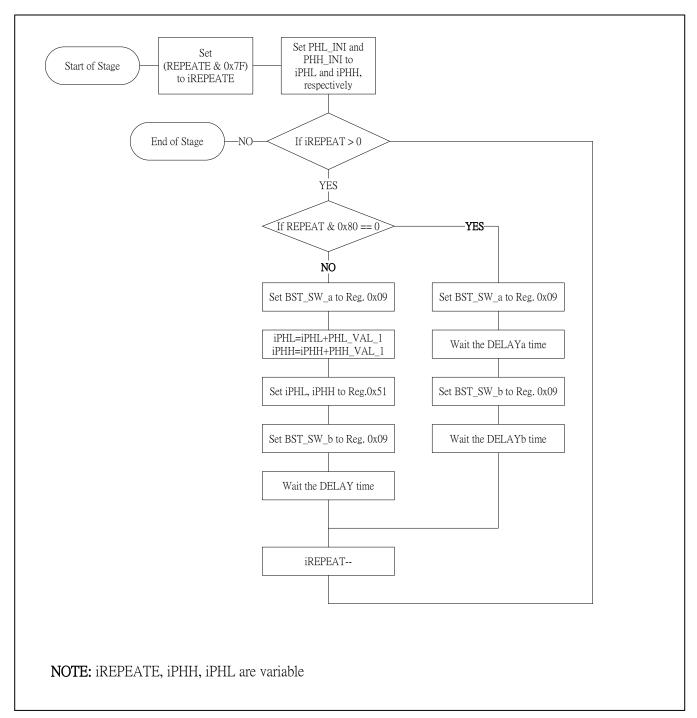

# 3.3 DC/DC soft-start

There are 32-bytes data for describing the sequence of soft-start.

|      | 0/8 | 1/9       | 2/10 | 3/11  | 4/12 | 5/13 | 6/14 | 7/15 |  |  |

|------|-----|-----------|------|-------|------|------|------|------|--|--|

|      |     |           |      |       |      |      |      |      |  |  |

| 0x20 |     |           |      | 1st s | tage |      |      |      |  |  |

| 0x28 |     | 2nd stage |      |       |      |      |      |      |  |  |

| 0x30 |     | 3rd stage |      |       |      |      |      |      |  |  |

| 0x38 |     | 4th stage |      |       |      |      |      |      |  |  |

|      |     |           |      |       |      |      |      |      |  |  |

The sequence totally has 4 stages. Each stage has 8 byte parameters. The bytes of each stage can be interpreted in 2 ways.

Data structure and definition:

|         | 1st byte      | 2nd byte | 3rd byte | 4th byte | 5th byte | 6th byte | 7th byte | 8th byte |

|---------|---------------|----------|----------|----------|----------|----------|----------|----------|

| format1 | REPEAT/FORMAT | PHL_INI  | PHH_INI  | PHL_VAR  | PHH_VAR  | BST_SW_a | BST_SW_b | DELAY    |

| format2 | REPEAT/FORMAT | BST_SW_a | BST_SW_b | DELAY_a  | DELAY_b  | ?        | ?        | ?        |

## **REPEAT/FORMAT:**

The times to repeat and the data format used in this stage

The MSB defines the format used in this stage

| bit           | 7      | 6 | 5 | 4   | 3         | 2   | 1 | 0 |

|---------------|--------|---|---|-----|-----------|-----|---|---|

| REPEAT/FORMAT | Format |   |   | Tim | es to rep | eat |   |   |

Format: 1-> bytes are defined as "format1"(see above)

0-> bytes are defined as "format2"(see above)

Example: 0x87 -> format1, repeat 7 times

0x64 -> format2, repeat 100 times

#### PHL INI:

Define the initial value of PHL(the first data of the reg.0x51)

#### PHH\_INI:

Define the initial value of PHH(the second data of the reg.0x51)

#### PHL VAR:

The byte represents the changing value of PHL with each iteration(REPEAT)

#### PHH\_VAR:

The byte represents the changing value of PHH with each iteration(REPEAT)

Both PHL\_VAR\_n and PHH\_VAR\_n could be a negative number. The negative number is represented by 2's complement.

Example: -5 equals 0xFB

Rev.: 01 Page: 19 of 26 Date: 2020/10/5

# BST\_SW\_a:

BST\_SW setting is the power on/off manager(reg.0x09) at the start of the phase.

#### **BST\_SW\_b**:

BST\_SW setting is the power on/off manager(reg.0x09) at the end of the phase.

#### **DELAY:**

The delay time at the end of the stage.

| bit     | 7     | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-------|------------|---|---|---|---|---|---|

| DELAY_r | Scale | Delay time |   |   |   |   |   |   |

Scale: 1 -> the scale of the delay time is msec.

0 -> the scale of the delay time is 10usec.

Example: 0x82 -> delay 2ms

0x02 -> delay 20us

#### **DELAY\_a:**

Same as "DELAY" but inserted after BST\_SW\_a

#### **DELAY** b:

Same as "DELAY" but inserted after BST\_SW\_b

Rev.: 01 Page: 20 of 26 Date: 2020/10/5

# Following is the flowchart for each "stage",

Rev.: 01 Page: 21 of 26 Date: 2020/10/5

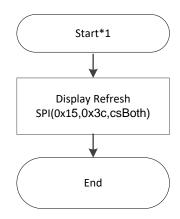

# 4 Send updating command

#### Note:

1. Start

Follow the end of the COG initial flow

Rev.: 01 Page: 22 of 26 Date: 2020/10/5

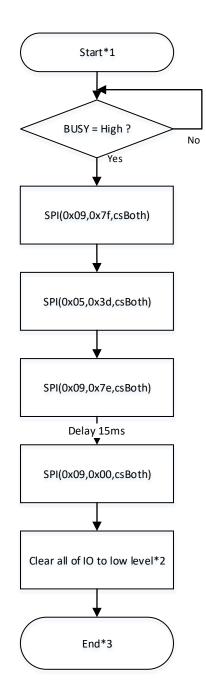

# 5 Turn-off DC/DC

#### Note:

1. Start

Follow the end of the send updating command

- 2. VCC/VDD, RESETB, A0, M\_CSB, S\_CSB, SCL and SDA

- 3. Finished the all of the steps for update the 12" EPD

Rev.: 01 Page: 23 of 26 Date: 2020/10/5

# Copyright

Pervasive Displays Incorporated All rights reserved.

This document is the exclusive property of Pervasive Displays Inc. (PDI) and shall not be reproduced or copied or transformed to any other format without prior permission of PDI. (PDI Confidential)

本資料為龍亭新技股份有限公司專有之財產,非經許可,不得複製、翻印或轉變成其他形式使用。

龍亭新技股份有限公司 Pervasive Displays Inc.

4F, No. 28, Chuangye Rd., Tainan Science Park, Tainan City 74144, Taiwan (R.O.C.)

Tel: +886-6-279-5399

http://www.pervasivedisplays.com

Rev.: 01 Page: 24 of 26 Date: 2020/10/5

# **Revision History**

| Version | Date      | Page<br>(New) | Section | Description            |

|---------|-----------|---------------|---------|------------------------|

| 01      | 2020/10/5 |               |         | First official edition |

|         |           |               |         |                        |

|         |           |               |         |                        |

|         |           |               |         |                        |

|         |           |               |         |                        |

|         |           |               |         |                        |

|         |           |               |         |                        |

Rev.: 01 Page: 25 of 26 Date: 2020/10/5

# **Glossary of Acronyms**

EPD Electrophoretic Display (e-Paper Display)

EPD Panel EPD

TCon Timing Controller

FPL Front Plane Laminate (e-Paper Film)

SPI Serial Peripheral Interface

COG Chip on Glass

PDI, PDi Pervasive Displays Incorporated

Rev.: 01 Page: 26 of 26 Date: 2020/10/5