# **EPD Driving Circuit**

Rev. 02 (Oct 2025)

#### **Preface**

This document introduces the driving reference circuit with the full range of EPDs with the iTC (internal timing controller) driver.

For EPDs with eTC (external timing controller) drivers, please refer to another document or contact us.

# Copyright

Pervasive Displays Incorporated All rights reserved. 龍亭新技股份有限公司 Pervasive Displays Inc. (PDI) <a href="https://www.pervasivedisplays.com">https://www.pervasivedisplays.com</a> 4F, No. 28, Chuangye Rd., Tainan Science Park, Tainan City 74144, Taiwan (R.O.C.)

Tel: +886-6-279-5399

## Index

| 1. | Application circuit block diagram | 2  |

|----|-----------------------------------|----|

|    |                                   |    |

| 2. | EPD driving circuit               | 3  |

|    |                                   |    |

| 3. | Terminal pin assignment           | 6  |

| -  |                                   |    |

| 1  | ROM.                              | 10 |

# **Glossary of Acronyms**

EPD Electrophoretic Display (e-Paper Display)

EPD Panel EPD

EPD Module EPD with TCon board

MCU Microcontroller Unit

FPC Flexible Printed Circuit

FPL Front Plane Laminate, E ink material film

SPI Serial Peripheral Interface

COG Chip on Glass, driver IC

PDI Pervasive Displays Incorporated

PCBA Printed Circuit Board Assembly

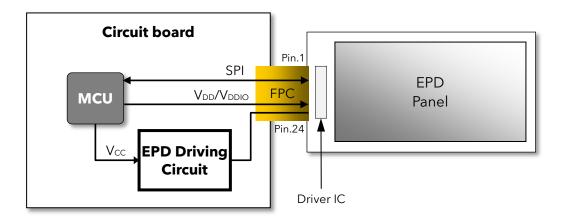

# 1. Application circuit block diagram

To work with our EPD panels, please follow the EPD driving circuit below on your PCBA. All components and circuits are necessary.

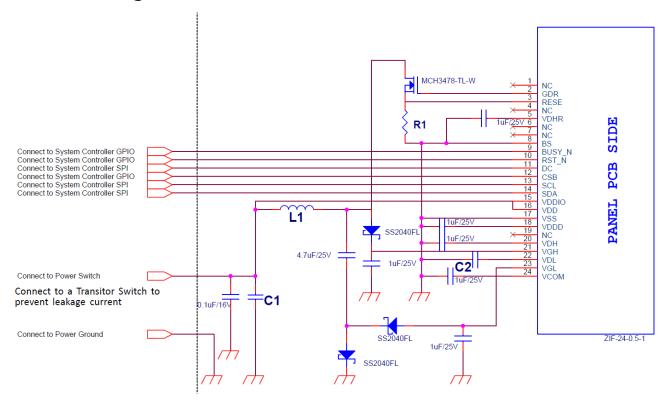

# 2. EPD driving circuit

## • EPD group

| Group | EPD sizes                                      |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|

| G1    | 1.52",1.54", 2.06", 2.13", 2.66", 2.71", 2.90" |  |  |  |  |  |

| G2    | 3.7", 4.2", 4.37"                              |  |  |  |  |  |

| G3    | 3.4", 5.81", 7.4", 9.7", 12"                   |  |  |  |  |  |

## • Specification of specific components

| Group | EPD group | Specification |           |  |

|-------|-----------|---------------|-----------|--|

| L1    | G1, G2    | 10µH          | (default) |  |

| LI    | G3        | 47µH          |           |  |

| D4    | G1, G2    | 0.47ohm       | (default) |  |

| R1    | G3        | 0R ohm/1%     |           |  |

| C1    | G1        | 1μF / 6.3V    |           |  |

| Ci    | G2, G3    | 4.7µF / 6.3V  | (default) |  |

| C2    | G1, G2    | 1μF / 25V     | (default) |  |

| C2    | G3        | 0.47µF / 25V  |           |  |

Note: if your circuit will support to drive multiple sizes of EPD, please use the default specifications.

## Other component specifications

| Туре           | Type Specification                        |          |  |  |

|----------------|-------------------------------------------|----------|--|--|

| Inductor       | 10uH ATNR4010100MT ±20% 0.8A              | ARLITECH |  |  |

| inductor       | 47uH ETPRH3D16B-470M 0.3A                 | ARLITECH |  |  |

|                | Si1308EDL or Si2300DS, SOT-23 N-Channel   | Vishay   |  |  |

| Transistar (1) | MCH3478, SOT-23 N-Channel                 | ON-Semi  |  |  |

| Transistor (1) | PMV100ENEAR or PMCB60XN, SOT-23 N-Channel | Nexperia |  |  |

|                | DMN3053L, SOT-23 N-Channel                | Diodes   |  |  |

| Diode (2)      | SS2040FL SOD-123FL                        | PANJIT   |  |  |

| Capacitors     | 25V 0603                                  |          |  |  |

#### Note:

- (1) Si1308EDL, MCH3478 or PJ2306 is a N-Channel Power MOSFET. The specification of selection criteria is  $R_{DS}{<}200m$  ohm (the lower the better),  $V_{DDS}{=}30V, V_{GS}{<}2.5V@I_d{=}0.5A$  or less.

- (2) SS2040FL is a Schottky diode needs the  $V_F$  as lower as possible, e.g. 0.2 to 0.4V and the repetitive peak reverse voltage > 25V.

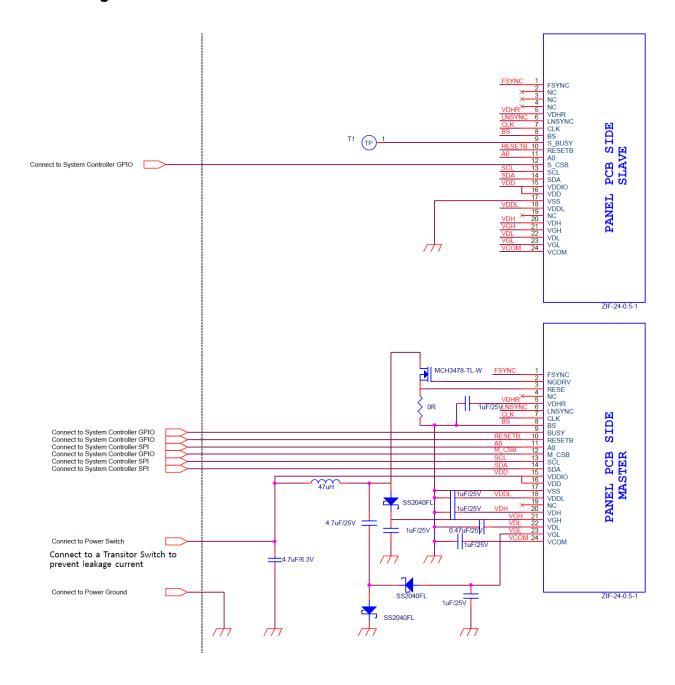

## Driving circuit for 9.7" or 12" models with 2 FPCs

# 3. Terminal pin assignment

# • FPC specification

| ltem          | Pin numbers | Pitch  | ZIF Connector                          |

|---------------|-------------|--------|----------------------------------------|

| Golden finger | 24          | 0.5 mm | HRS FH34SRJ 24S or<br>STARCONN 6700S24 |

# • Pin assignment

| 1 in assignment |              |      |                             |                                                                                                                                                    |  |  |

|-----------------|--------------|------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| No.             | Signal       | Туре | Connected to                | Function                                                                                                                                           |  |  |

| 1               | NC           | -    | -                           | Not connected                                                                                                                                      |  |  |

| 2               | GDR          | 0    | Power MOSFET driver control | This pin is the N-Channel MOSFET Gate Drive Control.                                                                                               |  |  |

| 3               | RESE         | I    | Booster control Input       | This pin is the Current Sense Input for the Control Loop.                                                                                          |  |  |

| 4               | NC           | -    | -                           | Not connected                                                                                                                                      |  |  |

| 5               | VDHR         | С    | Capacitor                   | This pin is the Positive Gate driving voltage and the Power Supply pin for VDHR. A stabilizing capacitor should be connected between VDHR and GND. |  |  |

| 6               | NC           | -    | -                           | Not connected                                                                                                                                      |  |  |

| 7               | NC           | -    | -                           | Not connected                                                                                                                                      |  |  |

| 8               | BS           | I    | VSS                         | This pin is for SPI type selection                                                                                                                 |  |  |

| 9               | BUSY_N       | 0    | Device Busy Signal          | This pin is Busy state output pin.  When Busy is Low, the operation of the chip should not be interrupted, and command should not be sent.         |  |  |

| 10              | RST_N        | I    | System Reset                | This pin is reset signal input.  Active Low.                                                                                                       |  |  |

| 11              | DC           | 1    | VDDIO or VSS                | This pin is Data/Command control.                                                                                                                  |  |  |

| 12              | CSB          | I    | VDDIO or VSS                | This pin is the chip select.                                                                                                                       |  |  |

| 13              | SCL          | I    | Data Bus                    | Serial communication clock input.                                                                                                                  |  |  |

| 14              | SDA          | 1    | Data Bus                    | Serial communication data input/output.                                                                                                            |  |  |

| 15              | VDDIO        | Р    | Power Supply                | Power for interface logic pins & I/O. It should be connected with VDDIO.                                                                           |  |  |

| 16              | VDD          | Р    | Power Supply                | Power Supply for the chip.                                                                                                                         |  |  |

| 17              | VSS<br>(GND) | Р    | Ground                      | Ground                                                                                                                                             |  |  |

| 18              | VDDD         | С    | Capacitor                   | Internal regulator output A capacitor should be connected between VDDD and GND.                                                                    |  |  |

| 19              | NC           | -    | -                           | Not connected                                                                                                                                      |  |  |

| 20              | VDH          | С    | Capacitor                   | This pin is the Positive Source driving voltage. A stabilizing capacitor should be connected between                                               |  |  |

|    |      |   |           | VDH and GND.                                                                                                      |

|----|------|---|-----------|-------------------------------------------------------------------------------------------------------------------|

| 21 | VGH  | С | Capacitor | This pin is the Positive Gate driving voltage. A stabilizing capacitor should be connected between VGH and GND.   |

| 22 | VDL  | С | Capacitor | This pin is the Negative Source driving voltage. A stabilizing capacitor should be connected between VDL and GND. |

| 23 | VGL  | С | Capacitor | This pin is the Negative Gate driving voltage. A stabilizing capacitor should be connected between VGL and GND.   |

| 24 | VCOM | С | Capacitor | This pin is the VCOM driving voltage A stabilizing capacitor should be connected between VCOM and GND.            |

Type: I=Input, O=Output, C=Capacitor, P=Power

# • Pin assignment for 9.7" or 12" where has 2 FPCs

## Master FPC

| No. | Signal           | Туре | Connected to                   | Function                                                                                                                                                     |  |

|-----|------------------|------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | FSYNC            | 1/0  | Slave FSYNC                    | Cascade line frame sync                                                                                                                                      |  |

| 2   | NGDRV            | 0    | Power MOSFET<br>Driver control | This pin is the N-Channel MOSFET Gate Drive Control.                                                                                                         |  |

| 3   | RESE             | I    | Booster Control<br>Input       | This pin is the Current Sense Input for the Control Loop.                                                                                                    |  |

| 4   | INTERNAL_V<br>PP | Р    | VPP PIN & Slave<br>FPC         | MTP power internal                                                                                                                                           |  |

| 5   | NC               | С    | -                              | NC                                                                                                                                                           |  |

| 6   | LNSYNC           | I/O  | Slave LNSYNC                   | Cascade line sync                                                                                                                                            |  |

| 7   | CLK              | I/O  | Slave CLK                      | Cascade clock                                                                                                                                                |  |

| 8   | BS               | I    | VSS                            | This pin is for SPI type selection                                                                                                                           |  |

| 9   | M_BUSY           | 0    | Device Busy<br>Signal          | This pin is Busy state output pin of the master chip. When Busy is Low, the operation of the chip should not be interrupted, and Command should not be sent. |  |

| 10  | RESETB           | 1    | System Reset                   | This pin is reset signal input. Active Low.                                                                                                                  |  |

| 11  | A0               | I    | VDDIO or VSS                   | This pin is Data/Command control.                                                                                                                            |  |

| 12  | M_CSB            | I    | VDDIO or VSS                   | This pin is the Master chip select.                                                                                                                          |  |

| 13  | SCL              | I    | Data Bus                       | Serial communication clock input.                                                                                                                            |  |

| 14  | SDA              | I    | Data Bus                       | Serial communication data input/output.                                                                                                                      |  |

| 15  | VDDIO            | Р    | Power Supply                   | Power for interface logic pins & I/O. It should be connected with VDDIO.                                                                                     |  |

| 16  | VDD              | Р    | Power Supply                   | Power Supply for the chip.                                                                                                                                   |  |

| 17  | VSS              | Р    | Ground                         | Ground                                                                                                                                                       |  |

| 18  | VDDL             | С    | Capacitor                      | Internal regulator output A capacitor should be connected between VDDL and VSS.                                                                              |  |

| 19 | NC   | - | -         | Not connected                                                                                                     |

|----|------|---|-----------|-------------------------------------------------------------------------------------------------------------------|

| 20 | VDH  | С | Capacitor | This pin is the Positive Source driving voltage. A stabilizing capacitor should be connected between VDH and VSS. |

| 21 | VGH  | С | Capacitor | This pin is the Positive Gate driving voltage. A stabilizing capacitor should be connected between VGH and VSS.   |

| 22 | VDL  | С | Capacitor | This pin is the Negative Source driving voltage. A stabilizing capacitor should be connected between VDL and VSS. |

| 23 | VGL  | С | Capacitor | This pin is the Negative Gate driving voltage. A stabilizing capacitor should be connected between VGL and VSS.   |

| 24 | VCOM | С | Capacitor | This pin is the VCOM driving voltage A stabilizing capacitor should be connected between VCOM and VSS.            |

## o Slave FPC

| No. | Signal | Туре | Connected to          | Function                                                                                                                                                    |  |

|-----|--------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | FSYNC  | I/O  | Master FSYNC          | Cascade line frame sync                                                                                                                                     |  |

| 2   | NC     | -    | -                     | Not connected                                                                                                                                               |  |

| 3   | NC     | -    | -                     | Not connected                                                                                                                                               |  |

| 4   | NC     | -    | -                     | Not connected                                                                                                                                               |  |

| 5   | NC     | -    | -                     | Not connected                                                                                                                                               |  |

| 6   | LNSYNC | I/O  | Master LNSYNC         | Cascade line sync                                                                                                                                           |  |

| 7   | CLK    | I/O  | Master CLK            | Cascade clock                                                                                                                                               |  |

| 8   | BS     | I    | VSS                   | This pin is for SPI type selection                                                                                                                          |  |

| 9   | S_BUSY | 0    | Device Busy<br>Signal | This pin is Busy state output pin of the slave chip. When Busy is Low, the operation of the chip should not be interrupted, and Command should not be sent. |  |

| 10  | RESETB | I    | System Reset          | This pin is reset signal input. Active Low.                                                                                                                 |  |

| 11  | A0     | 1    | VDDIO or VSS          | This pin is Data/Command control.                                                                                                                           |  |

| 12  | S_CSB  | I    | VDDIO or VSS          | This pin is the Slave chip select.                                                                                                                          |  |

| 13  | SCL    | I    | Data Bus              | Serial communication clock input.                                                                                                                           |  |

| 14  | SDA    | I    | Data Bus              | Serial communication data input/output.                                                                                                                     |  |

| 15  | VDDIO  | Р    | Power Supply          | Power for interface logic pins & I/O. It should be connected with VDDIO.                                                                                    |  |

| 16  | VDD    | Р    | Power Supply          | Power Supply for the chip.                                                                                                                                  |  |

| 17  | VSS    | Р    | Ground                | Ground                                                                                                                                                      |  |

| 18  | VDDL   | С    | Capacitor             | Internal regulator output A capacitor should be connected between VDDL and VSS.                                                                             |  |

| 19 | NC   | - | -         | Not connected                                                                                                        |

|----|------|---|-----------|----------------------------------------------------------------------------------------------------------------------|

| 20 | VDH  | С | Capacitor | This pin is the Positive Source driving voltage. A stabilizing capacitor should be connected between VDH and VSS.    |

| 21 | VGH  | С | Capacitor | This pin is the Positive Gate driving voltage<br>A stabilizing capacitor should be connected between<br>VGH and VSS. |

| 22 | VDL  | С | Capacitor | This pin is the Negative Source driving voltage. A stabilizing capacitor should be connected between VDL and VSS.    |

| 23 | VGL  | С | Capacitor | This pin is the Negative Gate driving voltage. A stabilizing capacitor should be connected between VGL and VSS.      |

| 24 | VCOM | С | Capacitor | This pin is the VCOM driving voltage A stabilizing capacitor should be connected between VCOM and VSS.               |

# **4.** BOM

| ltem | Description                                  | Vendor   | Q'ty   | Remark              |

|------|----------------------------------------------|----------|--------|---------------------|

| 1    | CAP 1uF 25V 0603 Y5V                         |          | 6 or 7 | 0603/1u/25V/Y       |

| 2    | CAP 4.7uF 25V 0603 Y5V                       |          | 1 or 2 | 0603/4.7u/25V/Y     |

| 3    | CAP 100nF 25V 0603 Y5V                       |          | 1      | 0603/100n/25V/Y     |

| 4    | DIODE SS2040FL SOD-123FL                     | PANJIT   | 3      | SS2040FL            |

| 5    | CONN 24P 6702A24-000000-G2-R<br>Pitch=0.5mm  | STARCONN | 1      | 6702A24-000000-G2-R |

| 6    | IND 10uH ATNR4010100MT +-20% 0.8A<br>H=0.9mm | ARLITECH | 0 or 1 | ATNR40100100MT/10u  |

| 7    | IND 47uH ATNR4047100MT +-20% 0.8A<br>H=0.9mm | ARLITECH | 0 or 1 | ATNR40470100MT/47u  |

| 8    | MOSFET MCH3478 SOT-23 N-Channel 30V/2A       | ON Semi. | 1      | MCH3478             |

| 9    | RES 0.47 ohm 0603 1% 1/10W                   |          | 1      | 0603/0.47R/1%       |